Product Summary

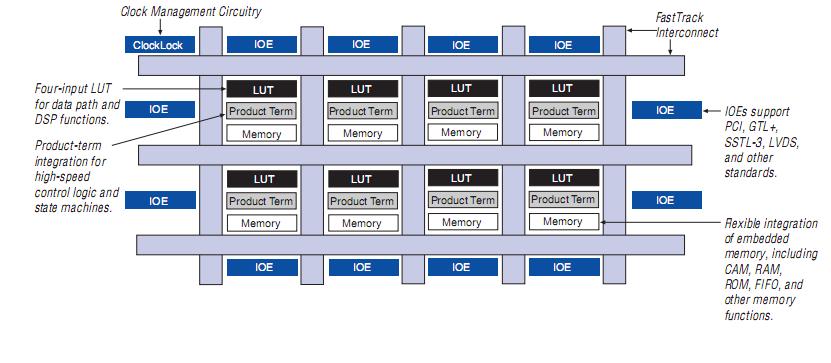

The EP20K100FC324-2N is a PLD, which is designed with the MultiCore architecture. It combines the strengths of LUT-based and productterm-based devices with an enhanced memory structure. LUT-based logic of the EP20K100FC324-2N provides optimized performance and efficiency for data-path, registerintensive, mathematical, or digital signal processing (DSP) designs. The EP20K100FC324-2N incorporates LUT-based logic, product-term-based logic, and memory into one device.

Parametrics

EP20K100FC324-2N absolute maximum ratings: (1)Supply voltage: –0.5 to 3.6 V With respect to ground; (2)DC input voltage: –2.0 to 5.75 V; (3)DC output current, per pin: –25 to 25 mA; (4)Storage temperature No bias: –65 to 150 ℃; (5)Ambient temperature Under bias: –65 to 135 ℃; (6)Junction temperature PQFP, RQFP, TQFP, and BGA packages, under bias: 135 ℃, Ceramic PGA packages, under bias: 150 ℃.

Features

EP20K100FC324-2N features: (1)MultiCore architecture integrating look-up table (LUT) logic, product-term logic, and embedded memory; (2)LUT logic used for register-intensive functions; (3)Embedded system block (ESB) used to implement memory functions, including first-in first-out (FIFO) buffers, dual-port RAM, and content-addressable memory (CAM); (4)ESB implementation of product-term logic used for combinatorial-intensive functions.

Diagrams

|

EP2001-9R |

|

EURO-CASSETTE 120W 2X 5.1V |

Data Sheet |

|

|

||||||||||||

|

EP201 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

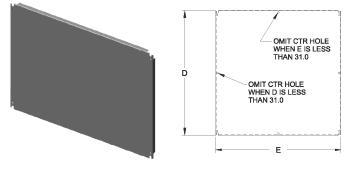

EP2012 |

Hammond Manufacturing |

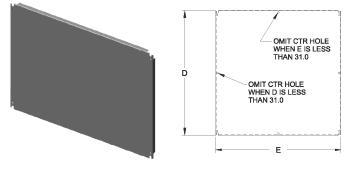

Electrical Enclosure Accessories E PANEL FITS 20X1224 |

Data Sheet |

Negotiable |

|

||||||||||||

|

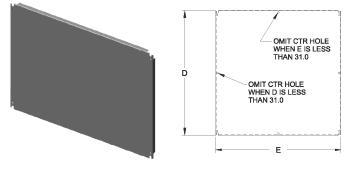

EP2016 |

Hammond Manufacturing |

Electrical Enclosure Accessories E-PANEL FITS 20 X 16 |

Data Sheet |

|

|

||||||||||||

|

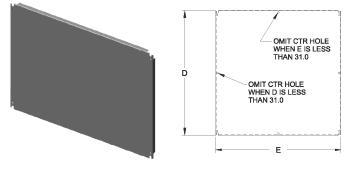

EP2020 |

Hammond Manufacturing |

Electrical Enclosure Accessories E-PANEL FITS 20 X 20 |

Data Sheet |

|

|

||||||||||||

|

EP2024 |

Hammond Manufacturing |

Electrical Enclosure Accessories E-PANEL FITS 20 X 24 |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))